fig10

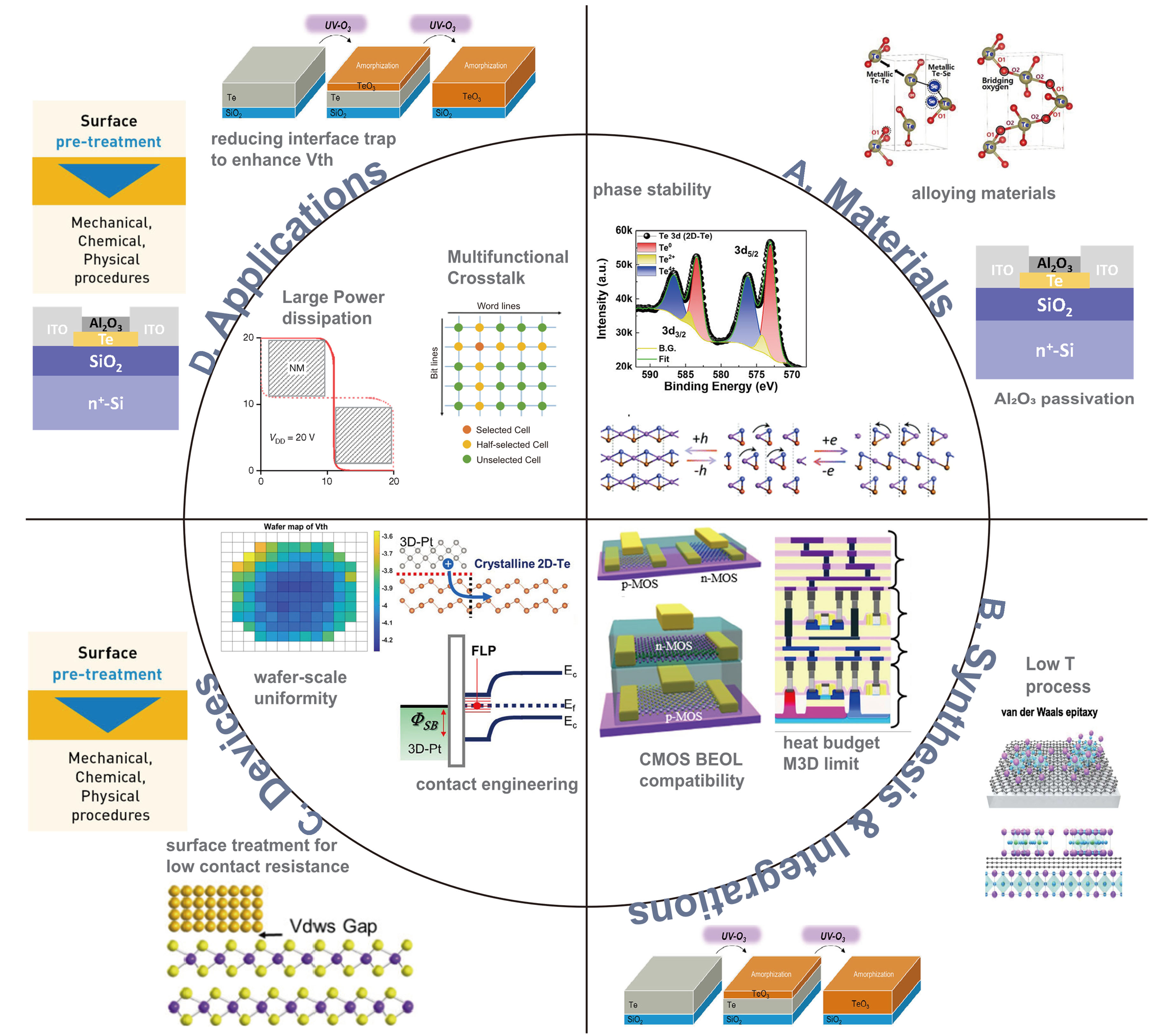

Figure 10. Challenges regarding (A) Materials: Te oxidation and phase stability; (B) Synthesis & Integration: Te-FET process compatibility with CMOS BEOL, heat limits in M3D processes; (C) Devices: wafer-scale uniformity, contact engineering to reduce contact resistance; (D) Applications: high power dissipation, multifunctional crosstalk at array scale. Figure 10A-D adapted from Refs.[19,22,56] with permission from © 2025 The Author(s). Advanced Materials, published by Wiley-VCH GmbH. FET: Field-effect transistor; CMOS: complementary metal-oxide semiconductor; BEOL: back-end-of-line; UV: ultraviolet; NM: noise margin; GND: ground; FLP: fermi level pinning; p-MOS: p-type metal oxide semiconductor.