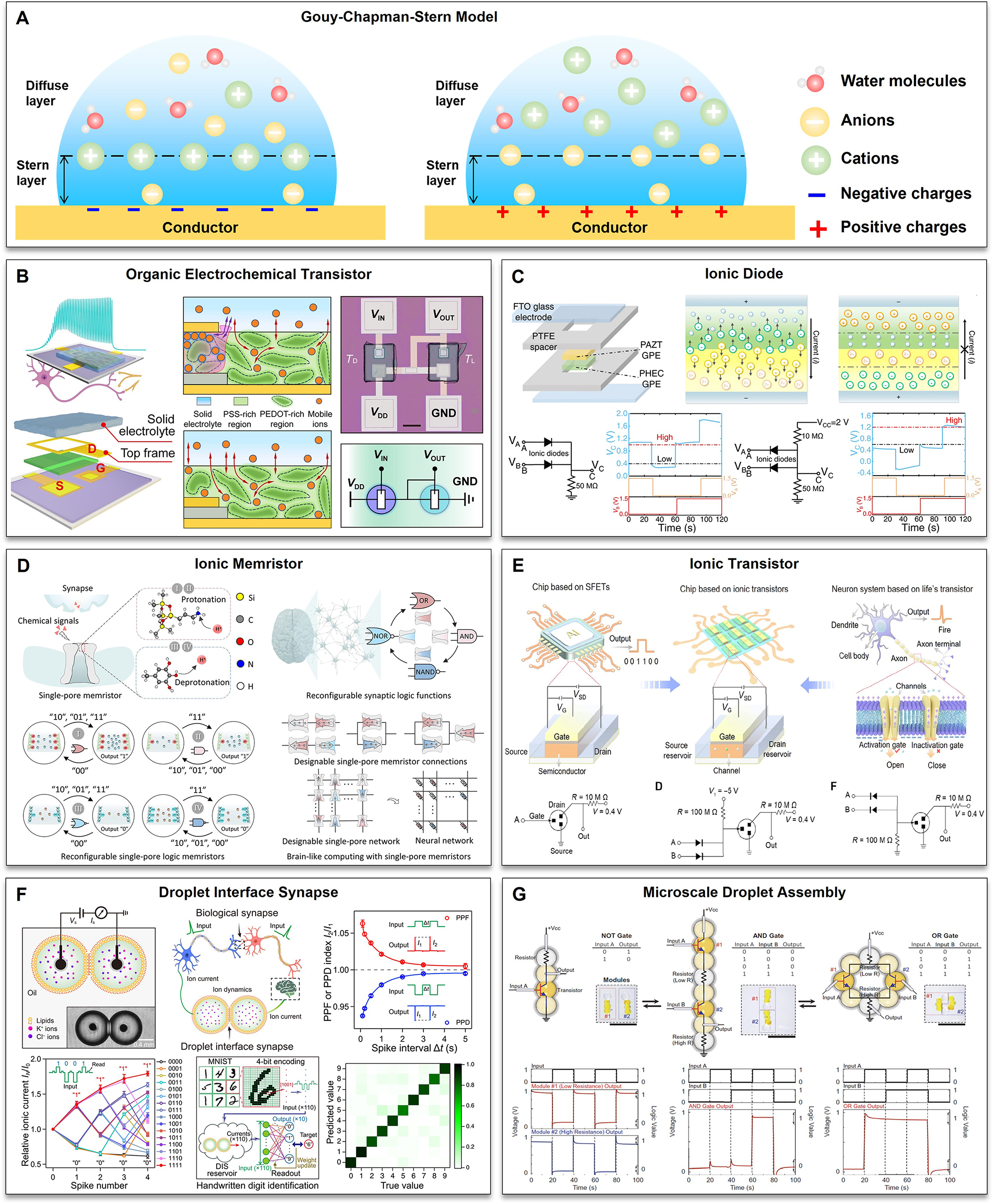

fig3

Figure 3. Iontronic logic enabled by dynamic regulation of EDLs at conductive interfaces. (A) GCS EDL model; (B) Organic electrochemical transistor. This figure is quoted with permission from the authors[36]; (C) Ionic diode. This figure is quoted with permission from the authors[37]; (D) Ionic memristor could realize OR, AND, NOR, and NAND logic gates. This figure is quoted with permission from the American Chemical Society[39]; (E) Ionic transistor. This figure is quoted with permission from American Chemical Society[40]; (F) Droplet interface synapse. This figure is quoted with permission from the American Association for the Advancement of Science[41]; (G) Microscale droplet assembly could realize NOT, AND, and OR logic gates. This figure is quoted with permission from The American Association for the Advancement of Science[42]. EDLs: Electrical double layers; EDL: electrical double layer; GCS: Gouy-Chapman-Stern; NOR: NOT OR gate; NAND: NOT AND gate; PSS: poly(styrenesulfonate); PEDOT: poly(3,4-ethylenedioxythiophene; GND: ground; SFETs: solid-state field-effect transistors; AI: artificial intelligence; PPF: paired-pulse facilitation; PPD: paired-pulse depression; MNIST: Modified National Institute of Standards and Technology database; DIS: droplet interface synapse.